### Design of a CMOS Op-Amp and Second Order Sigma Delta Analog to Digital Converter Using 0.18 µm CMOS Technology

Ashok Agarwal<sup>1</sup>, Sachin Rai<sup>2</sup> <sup>1</sup>·H.O.D of Dept. Electronics & Communication, JNCTS, R.G.P.V.University, Bhopal, India <sup>2</sup>Dept. of Electronics & Communication, JNCTS, R.G.P.V.University, Bhopal, India Email id: <sup>1</sup>ashok.jnct@gmail.com, <sup>2</sup>Sachinraisagar@gmail.com

Abstract: This paper presents the design of a CMOS OP-AMP and second order single bit Sigma-Delta Analog-to-Digital Converter (ADC) which is realized using CMOS technology. In this paper, of a CMOS OP-AMP and Second order Sigma-Delta ADC is designed which accepts an input signal of frequency 2 KHz, an OSR of 153, and 240 KHz sampling frequency. It is implemented in a standard 0.18um CMOS technology. The ADC operates at 0.7 V reference voltage. The Design and Simulation of the Modulator is done using Microwave offive sofware(9.1). This paper Sigma Delta Modulator. Op-amp which is a key componentused in the design, has the open loop voltage gain of 65db, Phase Margin of 44.5 Degree, output resistance of 130.5K $\Omega$ , and power dissipation of 0.096 mW. A CMOS OP-AMP and second order single bit Sigma Delta ADC is implemented using ±3.0 power supply and simulation results are plotted using Microwave offive sofware(9.1). After the modulator is designed, the output pulse train of the modulator is transferred from Microwave offive sofware(9.1) to MatlabWorkspace[9].

Keywords: Analog Circuit,2 stage CMOS Operational amplifie, High Frequency.

#### INTRODUCTION

With developments in deep sub micrometer CMOS processes, the available dynamic range in Operational Amplifiers (Op-Amps) is reduced due to lower power supply voltages [1]. The design of analog circuits such as operational amplifiers (Op-Amps) in CMOS technology becomes more critical. Many authors have noted the disproportionately large design time devoted to the analog circuitry in mixed mode integrated circuits. In this paper we introduce a new method for determining the component values and transistor dimensions for CMOS Op-Amps. The method handles a very wide variety of specifications and constraints, is extremely fast, and results in globally optimal designs[11]. In this paper, we present a systematic design methodology for split-length compensated low-voltage three-stage Op-Amps. The aim of the design methodology

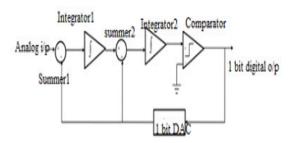

in this paper is to propose straightforward yet accurate equations for the design of high-gain 2 staged CMOS op-amp. To do this, a simple open-loop analysis with some meaningful parameters (phase margin, gainbandwidth, etc.) is performed. A sigma-delta modulator is one method for providing the front end to an analog to digital converter. When an analog signal is digitized, quantization error is introduced into the frequency The sigma-delta's function is to push the spectrum. quantization error that is near the signal into a higher frequency band near the sampling frequency. After this is done the signal can be low pass filtered and the original signal can be restored in a digitized form .The sigma-delta modulator with first order and second order noise shaping characteristics is designed The block diagram second order loop is shown in Figure 1.In the sigma-delta modulator, the difference between the analog input signal and the output of the DAC is the output of the Summer. This difference is given as an input to the Integrator. The integrator integrates each clock period.The clock at a much higher frequency than the input sinusoid, causing sine wave to be approximately flat over the clock period.

Fig 1: Block diagram of 2nd order sigma-delta modulator

#### II. CMOS TECHNOLOGY

In **CMOS** (Complementary Metal-Oxide Semiconductor) technology, both N-type and P-type transistors are used to realize logic functions. Today, CMOS technology is the dominant semiconductor technology for microprocessors, memories and application specific integrated circuits (ASICs). The main advantage of CMOS over NMOS and bipolar technology is the much smaller power dissipation. Unlike NMOS or bipolar circuits[4], a CMOS circuit has almost no static power dissipation. Power is only dissipated in case the circuit actually switches. This allows to integrate many more CMOS gates on an IC than in NMOS or bipolar technology, resulting in much better performance. An ntype MOS (NMOS) and a p-type MOS (PMOS) device are fabricated on the same p-doped wafer, with the PMOS device embedded in an n-doped well.

## III. SECOND STAGE OP-AMP AND ITS EXPERIMENTAL RESULT

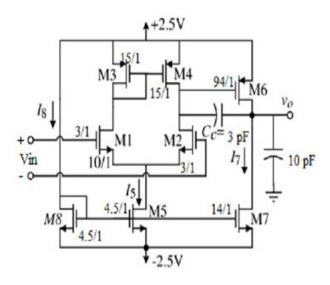

The operational amplifier that the integrator uses must have high gain to effectively carry out a smooth integration, as well as a large enough bandwidth to support the high frequency square waves that it will be integrating[6]. The amplifier used is shown in Figure 2.

Fig 2: Design Of Two Stage Op-amp

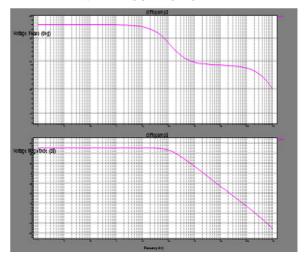

#### IV. RESULT OF OP-AMP

Figure 3. Gain and phase of a op-amp

| Parameter             | Two stage |

|-----------------------|-----------|

|                       | op amp    |

| Gain (dB)             | 65        |

| -3 dB frequency (MHz) | 19.8      |

|                       |           |

| Phase Margin (°)      | 44.5      |

| Unity gain frequency  | 65        |

| (GHz)                 |           |

| Power (mW)            | 0.096     |

Table 1:Parameters of Second Stage Op-Amp

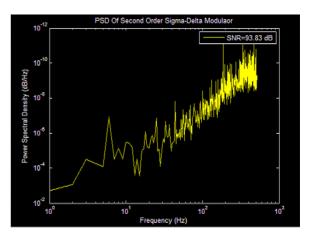

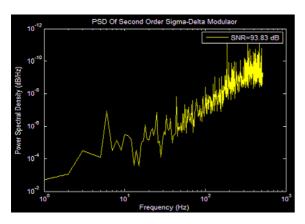

# V. SECOND ORDER SIGMA DELTA ADC CONVERTER AND ITS EXPERIMENTAL RESULT

Fig 4: PSD of 2nd order Modulator

ISSN: 2321 – 7529 (Online) | ISSN: 2321 – 7510 (Print)

V(int2)

V(output

V(output

V(output

V(output

V(output

V(output

V(output

V(output

V(output

V(output

V(output

V(output

V(output

V(output

V(output

V(output

Fig 5: Step by Step Performance of Second Order Modulator

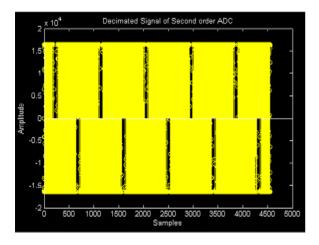

Fig 6: Decimated Output of Second Order Modulator.

Fig 7: PSD of 2nd order Modulator

#### VI. CONCLUSION

This project primarily aims to demonstrate the design of a OP-AMP and second order sigma-delta ADC to adapt to multiple communications standards. The simulated parameter for of a OP-AMP and second Order

International Journal of Research & Technology, Volume 1, Issue 1

Modulators using an integrator of capacitance 1nF and a Comparator with a propagation delay of 5 ns care shown below.

| Parameter | Second Order |

|-----------|--------------|

|           | Modulator    |

| SNR       | 90.13 dB     |

| ENOB      | 15its        |

| DR        | 135 dB       |

Table 2: Simulated Parametric Value

#### VII. FUTURE WORK

We can also change in NMOS design TSMC based on 0.18 CMOS Technology .The area which will be of interests optimizing the power distribution among the various blocks like continuous-time analog filter preceding the ADC, the ADC, and the digital filter following the ADC should be explored. We can also works on NMOS Transistor for increase gain and phase margin. We can also work on three stage of OP-AMP.

#### **REFERENCES**

- [1] M. A. Aguirre, J. Chávez, A. Torralba, and L. G. Franquelo, "Analog design optimization by means of a tabu search approach," in Proc. IEEE Int. Symp. Circuits Syst., vol. 1, 1994, pp. 375–378.

- [2] B.K Ahuja"An improved frequency compensation technique for CMOS operational amplifiers," IEEE J. Solid-State Circuits vol18,pp 629–633, Dec. 1983.

- [3] P. E. Allen and D. R. Holberg, CMOS Analog Circuit Design, 1<sup>st</sup> ed, U.K.: Oxford, 1987.

- [4] B.A. A. Antao, "Trends in CAD of analog ICs," IEEE Circuits Devices Mag., vol.12, no.5, pp. 31–41, Sept. 1996.

- [5] K. J. Antreich and H. E. Graeb, "Circuit optimization driven by worst-case distances," in Proc. IEEE Int. Conf. Computer-Aided Design ,1991, pp. 166–169.

- [6] J.Assael, P. Senn, and M. S.Tawfik, "A switched capacitor filter silicon compiler, "IEEE J. Solid-State Circuits, vol.23, pp. 166–174, Feb. 1988.

- [7] M. Avriel, R. Dembo, and U. Passy, "Solution of generalized geometric programs," Int. J. Numer. Methods Eng., vol. 9, pp. 149–168, 1975.

- [8] A. Barlow, K. Takasuka, Y. Nambu, T. Adachi, and J. Konno, "An integrated switched-capacitor filter design system," in Proc. IEEE Custom Integrated Circuit Conf., 1989, pp. 4.5.1–4.5.5.

- [9] C. S. Beightler and D. T. Phillips, Applied Geometric Programming. New York: Wiley,1976.

- [10] S. Boyd and L. Vandenberghe. (1997) Introduction to convex optimization with engineering applications. Stanford Univ.,Stanford, CA. [Online]http://www.stanford.edu/class/ee364/

- [11] R. K. Brayton, G. D. Hachtel, and A. Sangiovanni-Vincentelli, "A survey of optimization techniques for integrated-circuit design," Proc. IEEE ,vol. 69, pp. 1334–1362, Oct. 1981.

- [12] L. R. Carley, G. G. E. Gielen, R. A. Rutenbar, and W. M. C. Sansen, "Synthesis tools for mixed-signal ICs: Progress on frontend and back-end strategies," in Proc. 33rd Annu. Design Automation Conf., 1996, pp. 298–303.

- [13] L. R. Carley and R. A. Rutenbar, "How to automate analog IC designs," IEEE Spectrum, vol. 25, pp. 26–30, Aug. 1988.

- [14] International Journal of Advances in Engineering & Technology, July 2012. Vol.4, Issue 1, pp. 456-464

**1.**Ashok Agarwal-He is pursing Ph.d from mewar university. He passed M.Tech degree from R.G.P.V university. He has 9 years teaching experience in ECE department. His area of research are VLSI. He publish many paper on VLSI. He is working as the Professor(H.O.D) at JNCTS Bhopal.

**2.**Sachin Rai - Pursuing a M.Tech degree in VLSI Design from L.N.C.T. Bhopal . He is working as the Assistant Professor at JNCTS Bhopal.