# High Speed Area Efficient VLSI Architecture for Adaptive Filter using Multi-Rate Approach

<sup>1</sup>**Sourabh Rai, <sup>2</sup>Prof. Kamna Mishra**

M. Tech. Scholar, Department of Electronics and Communication, LNCT, Bhopal<sup>1</sup>

Assistant Professor, Department of Electronics and Communication, LNCT, Bhopal<sup>2</sup>

**Abstract**— More and more people around the world suffer from digital signal processing research field. The increase hardware complexity and increase area are the main reasons for this field. The multi-rate approach used for narrow band filter is designed and implemented in Xilinx software. The multi-rate approach is design using the decimator and interpolator structure in VHDL. Each structure is simulated using Xilinx software and compared the existing structure. The resulting structure is hardware efficient and consumes fewer slices compared to existing structure.

**Keywords:** - Filter Coefficient, Finite Impulse Response, Interpolation, Decimation

## I. INTRODUCTION

Versatile advanced separating has been a potential and adaptable method for sign preparing in a wide assortment of utilizations, for example, Channel Equalization, Noise Cancellation, Acoustic Echo Cancellation, Array Preparing, Linear Prediction and a few such different applications. The versatile components in most of these applications, have been Finite Impulse Response (FIR) channels, since they are steady and they more often than not combine to a worldwide least.

The mean square mistake (MSE) surfaces of FIR channels are quadratic capacities of filter coefficients and henceforth do not contain neighborhood minima (unimodal). Broad research completed on the conduct of FIR channels brought about the accessibility of many versatile calculations, for example, Widrow HofF Least Mean Square (LMS) calculation [1], Recursive Least Squares (RLS) calculation and its quick executions [2] and so forth., other than a class of change area and square handling calculations. In any case, when the drive reaction to be evaluated is long, the computational multifaceted nature of a versatile FIR channel turns out to be very costly for continuous applications and consequently in such circumstances, utilization of a shaft zero or Unbounded Impulse Response (HR) versatile channel turns into a need.

The enthusiasm on HR channels comes from the way that they offer potential favorable circumstances over the traditional FIR channels, for example, huge decrease in calculation for accomplishing a similar degree of execution and unrivaled demonstrating capacities of

physical frameworks, on the grounds that of the nearness of posts in the HR move work and thus versatile shaft zero separating has been a functioning territory of research over the most recent quite a long while [5]. Although, the posts make it conceivable to get well coordinated attributes with a significantly less lower request structure and thus with decreased computational weight, they are additionally primarily in charge of the downsides related with post zero channels, because of which reason they are as yet not considered as a dependable option in contrast to each of the zero channels. During the procedure of adjustment, the shafts may incidentally move outside the unit circle, making the channel precarious. Dependability observing winds up fundamental, to keep the shafts from refreshing outside the unit hover, especially in certain applications like reverberation crossing out, where the posts are known to be found nearer to the unit circle. This would necessitate that the post polynomial be figured, continuously and in every emphasis, to decide the posts that might have navigated outside the unit circle. Such an activity is very costly, from the calculation perspective, and whenever performed it will invalidate the computational advantage that the HR channels have over their FIR partners.

Further, the versatile HR calculations, all in all, offer generally slower assembly rate, in contrast with those of FIR calculations, as a result of the way that the HR channel yield and the MSE surface are non-straightly identified with the criticism coefficients. Other than these, the blunder surfaces of HR channels can contain numerous neighborhood minima [4], to which the versatile calculations could merge, prompting imperfect arrangements and this is in direct difference to that of non-recursive (FIR) channels, which consistently merge to a worldwide least. These issues have been serious enough to limit the across the board use of DR channels in modern and military applications, even till today.

## II. MULTIRATE APPROACH

Multirate frameworks give a progressively proficient handling of sign by means of resampling (up examining and down inspecting) of the first flag by a discretionary factor. The inspecting rates at different inner focuses can be kept as little as conceivable henceforth profoundly efficient multirate sign handling calculations are conceivable. Multirate frameworks can isolate in recurrence space the sign under thought into at least two

unique sign or it can create at least two extraordinary signals into a solitary sign.

To do the above works by and large examination - union framework is utilized. The examination part parts the sign. A channel forms a split sign. Depending on number of channels it is called two-channel or M-channel multirate channel bank. The job of amalgamation part is to roughly recreate the first sign. Multirate framework is one of the most energetic zones of research. This fame is merited in light of the wide scope of uses like resampling of sign for CD to DAT transformation, sub-band coding of sound signals[8][9], rate changing in multivariable advanced frameworks, reverberation crossing out, channel multiplexing, discourse combination and others. Multidimensional development is found in research of multi-rate frameworks like improvement of new methods for streamlining of mistake, improvement of effective multi-rate structures, advancement of multi-rate channel banks for non-uniform channels.. And so forth, yet look into in changed regions should be possible to structure effectively.

Alluring qualities of a general mistake rule for multirate frameworks are (A) fuse of most pessimistic scenario mistake from all sources, (B) consistency with the standard Chebyshev blunder paradigm for LTI channel structure, and (C) pertinence to a general class of inputs. The chebyshev paradigm is significant for some, reasons like it has a vitality portrayal, it is personally connected to reaction of framework to tones and it has moved toward becoming regular determination for channel plan. Section 2 offers prologue to mistake paradigm. In various sections of these proposal strategies like curved enhancement, H, streamlining are utilized for enhancing blunder. The benefits of these proposition are that they consider progress districts and certain requirements for channel structure.

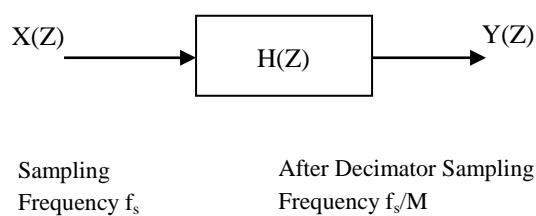

Fig. 1: Block Diagram of Decimator

$$H(Z) = \frac{X(Z)}{Y(Z)} = \frac{1}{M} \sum_{x=0}^{M-1} Z^{-x} \quad (1)$$

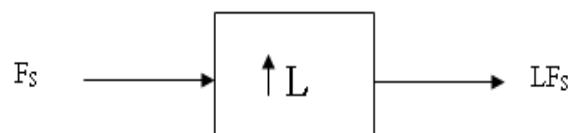

"Up sampling" is the way toward embeddings zero-esteemed examples between unique examples to expand the examining rate. (This is classified "zero-stuffing".) Up testing adds to the first flag undesired ghastly pictures

which are fixated on products [7] of the first inspecting rate.

"Introduction", in the DSP sense, is the procedure of up-examining pursued by sifting. (The separating evacuates the undesired phantom pictures.) As a straight procedure, the DSP feeling of insertion is to some degree not the same as the "math" feeling of addition, yet the outcome is reasonably comparable: to make "in the middle of" tests from the first examples.

The outcome is as though you had quite recently initially tested your flag at the higher rate. Expanding the inspecting recurrence use interpolator is present.

Since addition depends on zero-stuffing you can just interject by number components; you can't insert by fragmentary variables. (Be that as it may, you can join insertion and annihilation to accomplish a general sane.

Fig. 2: Interpolation with factor L

Factor, for instance, 4/5 up examining up desired phantom pictures to the flag at products of the first inspecting rate, so except if you expel those by separating, the up-tested flag [7] isn't equivalent to the first: it's contorted.

A few applications might have the capacity to endure that; for instance, if the pictures get expelled later by a simple channel, yet in many applications you should evacuate the undesired pictures through advanced sifting. Along these lines, introduction is undeniably increasingly normal [8] that up-inspecting alone.

### III. PROPOSED STRUCTURE

Implementation of multistage down sampling in general considers structural constraints, which reduce overall computation [5] required for design. Orthogonal and bi-orthogonal constraints imposed on filters will help in achieving perfect reconstruction. Multiple stages perform most processing at lower rates in order to improve efficiency. Design using constraints are useful for variety of applications like image processing, audio compression, and others [6].

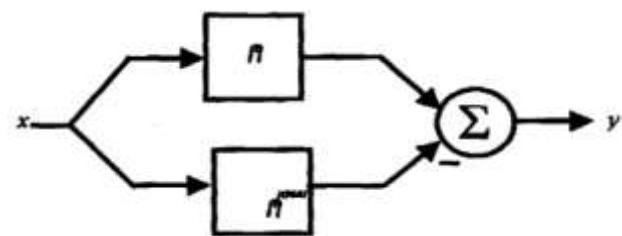

Fig. 3: Multi-rate model-matching problem

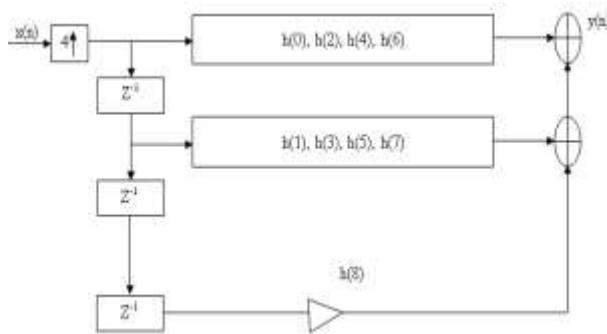

Fig. 4: Interpolator structure with filter order N=9 and L=4

Sampling frequency,

$$F_s = 250\text{Hz}$$

Pass band ripple,

$$\delta_p = 0.08\text{dB}$$

Stop band ripple,  $\delta_s = 42\text{dB}$

Pass band frequency,

$$f_p = .825\text{Hz}$$

Stop band frequency,

$$f_s = 4.15\text{Hz}$$

A typical need in gadgets and DSP is to confine a restricted band of frequencies from a more extensive data transmission flag. Narrowband channels rather catch just a little piece of the range. They are said to have a thin band-pass. The band-pass is basically the amount of the range the channel permits to pass. This is typically estimated in nanometers. Limited band channel comprises of decimator, restricted band and interpolator.

#### IV. SIMULATION RESULT

The proposed architecture has very low hardware complexity compared to direct approach based structures, because direct method requires more multiplier compare to proposed architecture. In the proposed architecture, calculate the decimator and interpolator structure for design a narrow band filter.

Table 1 shows the theoretical analysis of direct method & multi-rate approach for different filter coefficient and sampling frequency. Table 2 shows cell usage for the Comparison of Performance of the Proposed Implementation and the Existing Implementation of Narrow Band Filter.

Table 1: Comparison Result for Previous and Proposed Approach for N=5

|                      | Previous Approach | Proposed Approach |

|----------------------|-------------------|-------------------|

| Number of Slice      | 45                | 34                |

| Number of Flip Flops | 39                | 32                |

| No. of Slice LUTs    | 63                | 57                |

| MCPD (ns)            | 17.564            | 14.352            |

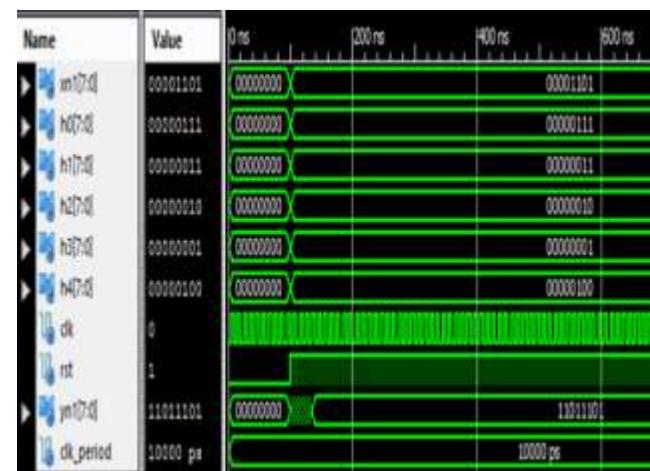

Fig. 5: Output Test Bench Waveform of Narrow Band Filter (Filter Coefficient N=5)

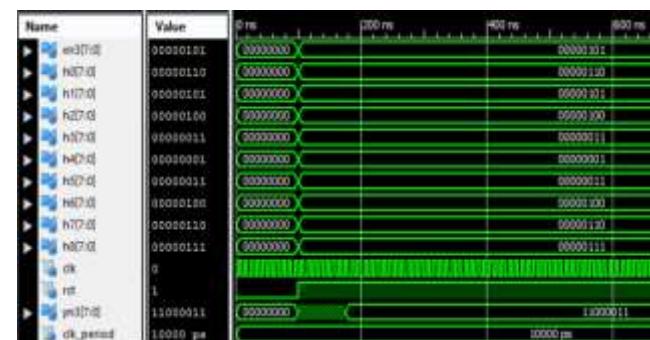

The design as were discussed in figure 3 and figure 4 were implemented using VHDL and then were tested on model sim to determine the number of slice and maximum high frequency. In figure 5, figure 6 and figure 7 have shown the output waveform of narrow band filter and chat between filter order and slices. In figure 7, compare the result between numbers of slice and filter order. Increase the filter order also increase the number of slice shown if figure 6.

Table 3: Comparison Result for Previous and Proposed Approach for N=9

|                      | Previous Approach | Proposed Approach |

|----------------------|-------------------|-------------------|

| Number of Slice      | 74                | 66                |

| Number of Flip Flops | 71                | 64                |

| No. of Slice LUTs    | 141               | 113               |

| MCPD (ns)            | 22.432            | 17.085            |

Fig. 6: Output Waveform of 9\_tap Narrow Band Filter

## V. CONCLUSION

The narrowband filter is realized in FIR filter. Based on the direct approach, the filter requires 150 filter coefficients to meet the desired frequency response. To implement such a large order FIR filter in hardware involves large resources and sometime difficult to implement in resource constrained application. Keeping this in view, we have used Multi-rate approach to design the narrowband filter. We have used down sampling factor 2 and 4 for this purpose and found that, down sampling factor 4 requires significantly less filter constants than 2. To implement the narrowband filter, we therefore chosen down sampling factor 4 and designed the decimator, interpolator and narrowband filter. The total number of filter coefficients required to realize the decimator, interpolator and the narrowband filter 64 which is almost 58% less than the direct method.

## REFERENCE

- [1] Basant K. Mohanty, Pramod Kumar Meher, and Sujit K. Patel, "LUT Optimization for Distributed Arithmetic-Based Block Least Mean Square Adaptive Filter", *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, IEEE 2016.

- [2] Ming Liu, Ming-Jiang Wang and Bo-Yang Song, "An efficient architecture of the sign-error LMS adaptive filter", *Solid-State and Integrated Circuit Technology (ICSICT), 13th IEEE International Conference on*, IEEE 2016.

- [3] Ch. Sravani and U. V Ratna Kumari, "Implementation fixed-point Least Mean Square adaptive filter for low area and delay", *Signal Processing, Communication, Power and Embedded System (SCOPES), International Conference on*, IEEE 2016.

- [4] Sireesha N, K. Chithra and Tata Sudhakar, "Performance analysis of linear recursive least squares adaptive filter to mitigate multipath effect", *Ocean Electronics (SYMPOL), 2015 International Symposium on*, IEEE 2015.

- [5] Raymond Lee, Mohammed A.S. Khalid and Esam Abdel-Raheem, "Configurable hardware implementation of a pipelined DNLMS adaptive filter", *Microelectronics (ICM), 26th International Conference on*, IEEE 2014.

- [6] P. Priya and P. Babu, "An efficient architecture for the adaptive filter using delayed LMS algorithm", *Information Communication and Embedded Systems (ICICES), 2014 International Conference on*, IEEE 2014.

- [7] S. Y. Park and P. K. Meher, "Low-power, high-throughput, and low-area adaptive FIR filter based on distributed arithmetic," *IEEE Trans. Circuits System- II, Exp. Briefs*, Vol. 60, No. 6, pp. 346-350, Jun. 2013.

- [8] B. K. Mohanty and P. K. Meher, "A high-performance energy-efficient architecture for FIR adaptive filter based on new distributed arithmetic formulation of block LMS algorithm," *IEEE Trans. Signal Process.*, vol. 61, no. 4, pp. 921-932, Feb. 2013.

- [9] Azadeh Safari and Yinan Kong "Four tap Daubechies filter banks based on RNS", *IEEE International Conference on Image Processing, Signal and System*, 2012.