# High Speed Energy-Efficient Carry Skip Adder High-Speed skips logic at different levels- A Review

Shadab Ahmad<sup>1</sup>, Prof. Suresh S Gawande<sup>2</sup>, Prof. Sher Singh<sup>3</sup>

Dept. Of ECE

Bhabha Engineering Research Institute

Bhopal, MP, India;

shadabahmadec@yahoo.com, suresh.gawande@rediffmail.com, shersinghagra@gmail.com

Abstract—In this paper, survey on a carry skip adder (CSKA) structure that contains a higher speed however lower energy consumption compared with the standard one. The speed improvement is achieved by applying concatenation and inculpation schemes to enhance the efficiency of the conventional CSKA (Conv-CSKA) structure. The projected hybrid variable latency CSKA reveal reduction within the power consumption compared with the most recent works during this field whereas having a reasonably high speed.

Keywords— Carry skip adder (CSKA), energy efficient, high performance, hybrid variable latency adders, voltage scaling

# I. INTRODUCTION

Digital multipliers are an indispensable component in general-purpose microprocessors, digital signal processors (DSPs), and multimedia application accelerators. Over the last two decades, we have witnessed an apparent paradigm shift and a surge of interest to explore alternative number representations for digital multiplier design [1]-[3], among which the redundant binary (RB) number [4], [5] has emerged as a key internal format to speed up the partial product accumulation of fast tree-structured parallel multipliers. The carry-free addition allows the partial products to be reduced at a rate of 2:1 using the RB adders as opposed to the 3:2 reduction rates with a full adder in the normal binary (NB) multiplier. In addition, the regular structure of the RB summing tree also makes RB multipliers amendable to areaefficient VLSI layout. Low-power, area-efficient, and highperformance VLSI systems are more and more utilized in portable and mobile devices, multi standard wireless receivers. and biomedical instrumentation [1]. An adder is that the main component of an arithmetic unit. A complex digital signal processing (DSP) system involves several adders. AN efficient adder design basically improves the performance of a complex DSP system. ADDERS are a key building block in arithmetic and logic units (ALUs) and thus increasing their speed and reducing their power/energy utilization strongly affect the speed and power utilization of processors. There are many works on the subject of optimizing the speed and Power of those units that are reported in. Obviously, it's extremely desirable to attain higher speeds at low-power/energy consumptions, which are a challenge for the designers of general purpose processors.

Design of area and power efficient high speed data path logic systems are one of the most substantial areas of research in VLSI system design. In digital adders, the speed of addition is limited by the time required propagate a carry through the

adder. The sum for each bit position in an elementary adder is generated sequentially only after the previous bit position has been summed and a carry propagated into the last position. One of the effective techniques to lower the power consumption of digital circuits is to reduce the supply voltage because of quadratic dependence of the switching energy on the voltage. Moreover, the sub threshold current, that is the main leakage component in OFF devices, has an exponential dependence on the supply voltage level through the draininduced barrier lowering impact. Depending on the amount of the supply voltage reduction, the operation of ON devices might reside in the super threshold, near-threshold, or sub threshold regions. Working in the super threshold region provides us with lower delay and higher switching and leakage powers compared with the near/sub threshold regions. In the sub threshold region, the gate delay and leakage power exhibit exponential dependences on the supply and threshold voltages. Moreover, these voltages are (potentially) subject to process and environmental variations in the nano-scale technologies. The variations increase uncertainties in the said performance parameters. Additionally, the small sub threshold current causes a large delay for the circuits operating in the sub threshold region.

Recently, the near-threshold region has been thought of as a part that gives a further desirable trade-off purpose between delay and power dissipation compared with that of the sub threshold one, as a results of it ends up in lower delay compared with the sub-threshold region and considerably lowers shift and leak powers compared with the super threshold region. in addition, near-threshold operation, that uses offer voltage, levels near the threshold voltage of transistors, suffers considerably less from the method and environmental variations compared with the sub threshold region. Over the past four decades, the amount of transistors on a chip has increased exponentially in accordance with Moore's law [1]. This has LED to progress in diversified computing applications, like health care, education, security, and communications. Variety of social projections and industrial roadmaps are driven by the expectation that these rates of improvement can continue, however the impediments to growth are additional formidable these days than ever before. The most important of these barriers is related to energy and power dissipation, and it's not an exaggeration to state that developing energy-efficient solutions is important to the survival of the semiconductor business. Extensions of today's solutions will only go up to now, and while not enhancements in energy potency, CMOS is in danger of running out of steam.

# II. LITERATURE SURVEY

Milad Bahadori et. al [1] "High-Speed and Energy-Efficient Carry Skip Adder Operating Under a Wide Range of Supply Voltage Levels", in this paper planned carry skip adder (CSKA) structure that has a better speed yet lower energy consumption compared with the standard one. The speed improvement is achieved by applying concatenation and incrimination schemes to enhance the efficiency of the standard CSKA (Conv-CSKA) structure. In addition, rather than utilizing electronic device logic, the planned structure makes use of AND-OR-Invert (AOI) and OR-AND-Invert (OAI) compound gates for the skip logic. The structure is also realised with each fixed stage size and variable stage size styles, whereby the latter a lot of improves the speed and energy parameters of the adder. Finally, a hybrid variable latency extension of the planned structure, that lowers the ability consumption whereas not considerably impacting the speed, is presented. This extension utilizes a changed parallel structure for increasing the slack time, and hence, enabling extra voltage reduction. The planned structures are assessed by comparison their speed, power, and energy parameters with those of different adders using a 45-nm static CMOS technology for a good vary of give voltages during this paper, a static CMOS CSKA structure called CI-CSKA was planned, that exhibits a better speed and lower energy consumption compared with those of the standard one. The speed improvement was achieved by modifying the structure through the concatenation and incrimination techniques. In addition, AOI and OAI compound gates were exploited for the carry skip logics. The efficiency of the planned structure for each FSS and VSS was studied by comparison its power and delay with those of the Conv-CSKA, RCA, CIA, SQRT-CSLA, and KSA structures. The results revealed considerably lower PDP for the VSS implementation of the CI-CSKA structure over a good vary of voltage from super-threshold to close threshold.

Yajuan He et. al [2] "Power-Delay Efficient Hybrid Carry-Lookahead/Carry-Select Based Redundant Binary to Two's Complement Converter", in this paper projected shown that the inherent redundancy of rb encoding is totally exploited to alter and speed up the reverse conversion through a chic uniting of mixed-radix carry-lookahead network and novel carry-select adder. A hybrid CLA/CSL adder realization is well suited to the projected formulation of the reverse conversion downside. The carries of the CLA network are elite to equalize the essential path of the optimally designed CSL sections for a given quantity length. The carry generation network is enforced with heterogeneous CMOS cells, and also the CSL block is simplified while not jeopardizing the essential path delay by making use of the cluster carry-in signals generated by the structure CLA network. To any reduce the price of implementing the CSL, the ripple-carry adder chain is changed and incorporated with a new add-one circuit. we've got shown by means that of logical effort technique that the projected reverse device outperforms 3 alternative competitive converters in terms of delay, semiconductor device count and their product for quantity lengths vary from eight to 128 b. The speed improvement over alternative converters is a lot of provident with inflated quantity length. HSPICE simulation results of a 64-bit transistor-level implementation of our

projected device and also the best challenger obtained from the le delay model verified the superiority of our projected device.

By Dejan Markovic et. al [3] "Ultralow-Power Design in Near-Threshold Region", in this paper projected Computations in standard CMOS logic are restricted by sub threshold leakage. Minimum-energy purpose is very expensive in terms of performance, similar to minimum delay purpose is in terms of energy. we will gain 10-times in performance by increasing energy by 200th higher than MEP. the most dominant optimization variable around MEP is that the provide voltage, whereas time-multiplexing helps reduce area and leakage energy. Moderate inversion operation needs careful modeling and suggests new pass-transistor based logic vogue that may outperform standard CMOS within the near-threshold regime, by achieving the energy below MEP of normal CMOS. The use of time-multiplexing around MEP leads to each lower space and energy while not performance penalty, owing to reduced leakage that comes with a lower area. Voltage scaling AND circuit size techniques around MEP may be applied inside typical chip synthesis tools (in an ordered manner) to reduce each space and energy. We've got demonstrated energy efficiency of two GOPS/mW and area potency of twenty GOPS/mm2 during a 90-nm CMOS technology using the techniques described during this paper.

By Ronald G. Dreslinski et al [4] "Near-Threshold Computing: Reclaiming Moore's Law Through Energy Efficient Integrated Circuits", in this paper projected As Moore's law continues to produce designers with a lot of transistors on a chip, power budgets are beginning to limit the applicability of those further transistors in typical CMOS style. During this paper we tend to looked back at the feasibility of voltage scaling to reduce energy consumption. Though subthreshold operation is well known to supply substantial energy savings it's been relegated to some of applications because of the corresponding system performance degradation. we tend to then turned to the thought of near-threshold computing (NTC), wherever the availability voltage is at or near the switch voltage of the transistors. This regime allows energy savings on the order of 10X, with only a 10X degradation in performance, providing a way better energy/performance trade-off than subthreshold operation. The rest of the paper focused on the 3 major barriers to widespread adoption of NTC and current analysis to overcome them. The 3 barriers addressed were: 1) performance loss; 2) increased variation; and 3) increased functional failure. With traditional device scaling now not providing energy efficiency enhancements, our primary conclusion is that the answer to the current energy crisis is that the universal application of aggressive low-voltage operation, namely NTC, across all computation platforms.

Shailendra Jain et. al [5] "280mV-to-1.2V Wide-Operating-Range IA-32 Processor in 32nm CMOS", in this paper planned Near-threshold computing brings the promise of an order of magnitude improvement in energy efficiency over this generation of microprocessors [1]. However, frequency degradation because of aggressive voltage scaling might not be acceptable across all single-threaded or performance-constrained applications. Enabling the processor to control over a large voltage vary helps to achieve very best energy

efficiency whereas satisfying variable performance demands of the applications. This paper describes an IA-32 processor fabricated in 32nm CMOS technology [2], demonstrating a reliable ultra-low voltage operation and energy efficient performance across the wide voltage range from 280mV to 1.2V.

# III. METHOD

#### A. Conventional CSKA Structure

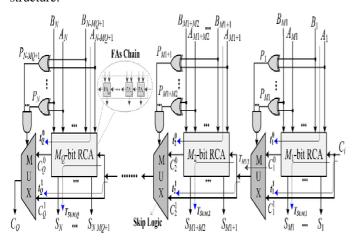

The conventional structure of the CSKA consists of stages containing chain of full adders (FAs) (RCA block) and 2:1 electronic device (carry skip logic). The RCA blocks are connected to every different through 2:1 multiplexers, which might be placed into one or additional level structures. The CSKA configuration (i.e., the quantity of the FAs per stage) has a great impact on the speed of this sort of adder. The structure of an N -bit Conv-CSKA, that is predicated on blocks of the RCA (RCA blocks), is shown in Fig. 1. Additionally to the chain of FAs in every stage, there's carry skip logic. For an RCA that contains N cascaded FAs, the worst propagation delay of the summation of 2 N -bit numbers, A and B, belongs to the case wherever all the FAs are within the propagation mode. It means worst case delay belongs to the case where

$$P_i = A_i \oplus B_i = 1$$

for  $i = 1, ...., N$

Where Pi is that the propagation signal associated with Ai and bi. This shows that the delay of the RCA is linearly associated with N. the N FAs of the CSKA are classified in Q stages. Every stage contains an RCA block with M j FAs ( j = 1, ..., Q) and a skip logic. In every stage, the inputs of the multiplexer (skip logic) are the carry input of the stage and also the carry output of its RCA block (FA chain). Additionally, the product of the propagation signals of the stage is employed because the selector signals of the electronic device. The CSKA could also be implemented using FSS and VSS wherever the best speed could also be obtained for the VSS structure.

Fig. 1 Conventional CSKA structure

# B. Carry lookaheadadder (CLA)

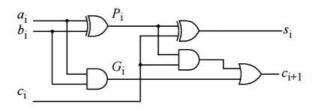

The carry lookahead adder (CLA) solves the carry delay disadvantage by calculative the carry signals before, based on the input signals. It's based on the particular fact that a carry signal are generated in two cases: (1) once each bits ai and bi are one, or (2) once one of the two bits is one and so the carryin is one. Thus, one will write.

$$c_{i+1} = a_i.b_i + (a_i \oplus b_i).c_i$$

$s_i = (a_i \oplus b_i) \oplus c_i$

The above two equations can be written in terms of two new signals  $p_i$  and  $g_i$ , which are shown in Figure 2:

Fig 2: Full adder at stage i with pi and gi shown

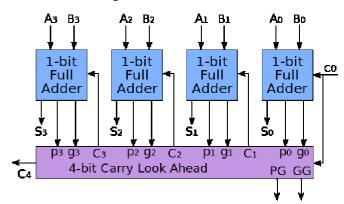

A carry-lookahead adder (CLA) or fast adder could be a variety of adder utilized in digital logic. A carry-lookahead adder improves speed by reducing the quantity of time needed to determine carry bits. It will be contrasted with the easier, however usually slower, ripple carry adder that the carry bit is calculated alongside the total bit, and every bit should wait till the previous carry has been calculated to start calculative its own result and carry bits (see adder for detail on ripple carry adders). The carry-lookahead adder calculates one or additional carry bits before the total that reduces the wait time to calculate the results of the larger value bits.

Fig. 3 Carry Look Ahead

# IV. CONCLUSION

This paper has reviewed the mainly latest research trends and proposed carry skip adder (CSKA). In this paper presented analyzed the speed enhancement is achieved by applying concatenation and incrimination schemes to improve the efficiency of the conventional CSKA (Conv-CSKA) structure. In this paper many different methods are studied for carry skip adder. In this paper proposed as a review to improve the

efficiency power carry skip adder. The speed enhancement was achieved by modifying the structure through the concatenation and incrimination techniques.

# REFERENCES

- [1] Milad Bahadori, Mehdi Kamal, Ali Afzali-Kusha "High-Speed and Energy-Efficient Carry Skip Adder Operating Under a Wide Range of Supply Voltage Levels", IEEE Transactions On Very Large Scale Integration (Vlsi) Systems 2015.

- [2] Yajuan He., Chip-Hong Chang "A Power-Delay Efficient Hybrid Carry-Lookahead/Carry-Select Based Redundant Binary To Two's Complement Converter", IEEE Transactions On Circuits And Systems—I: Regular Papers, Vol. 55, No. 1, February 2008.

- [3] By Dejan Markovic, Cheng C. Wang, Louis P. Alarco'n "Ultralow-Power Design in Near-Threshold Region", IEEE · March 2010.

- [4] By Ronald G. Dreslinski, Michael Wieckowski, David Blaauw "Near-Threshold Computing: Reclaiming Moore's Law Through Energy Efficient Integrated Circuits", IEEE Vol. 98, 0018-9219/\$26.00 2010 IEEE No. 2, February 2010.

- [5] Shailendra Jain, Surhud Khare, Satish Yada, Ambili V "A 280mV-to-1.2V Wide-Operating-Range IA-32 Processor in 32nm CMOS", IEEE International Solid-State Circuits Conference feb 2012.

- [6] I. Koren, Computer Arithmetic Algorithms, 2nd ed. Natick, MA, USA: A K Peters, Ltd., 2002.

- [7] R. Zlatanovici, S. Kao, and B. Nikolic, "Energy-delay optimization of 64-bit carry-lookahead adders with a 240 ps 90 nm CMOS design example," IEEE J. Solid-State Circuits, vol. 44, no. 2, pp. 569–583, Feb. 2009

- [8] S. K. Mathew, M. A. Anders, B. Bloechel, T. Nguyen, R. K. Krishnamurthy, and S. Borkar, "A 4-GHz 300-mW 64-bit integer execution ALU with dual supply voltages in 90-nm CMOS," IEEE J. Solid-State Circuits, vol. 40, no. 1, pp. 44–51, Jan. 2005.

- [9] V. G. Oklobdzija, B. R. Zeydel, H. Q. Dao, S. Mathew, and R. Krishnamurthy, "Comparison of high-performance VLSI adders in the energy-delay space," IEEE Trans. Very Large Scale Integr. (VLSI)Syst., vol. 13, no. 6, pp. 754–758, Jun. 2005.

- [10] B. Ramkumar and H. M. Kittur, "Low-power and area-efficient carry select adder," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 20, no. 2, pp. 371–375, Feb. 2012.

- [11] M. Vratonjic, B. R. Zeydel, and V. G. Oklobdzija, "Low- and ultra low-power arithmetic units: Design and comparison," in Proc. IEEEInt. Conf. Comput. Design, VLSI Comput. Process. (ICCD), Oct. 2005, pp. 249–252.

- [12] C. Nagendra, M. J. Irwin, and R. M. Owens, "Area-time-power tradeoffs in parallel adders," IEEE Trans. Circuits Syst. II, Analog Digit. SignalProcess., vol. 43, no. 10, pp. 689–702, Oct. 1996.