# Study of CMOS Technology based Different VLSI Circuit for Low Power Application

# Dr. Vijeta Yadav

Assistant Professor School of Electronics and Communication, Madhyanchal Professional University, Bhopal

Abstract- It is dynamic in the plot with the participation of the transmission portal. Dynamic potential is largely saved by using the minimum number of portable using the clock indicator in the overall path configuration. reducing both the capacitive load and the switching activity of the nodes inside the track. . By minimizing the load and loading each internal node compared to variations of the input data indicator, its potential depletion is further reduced. Threshold intensity drop is the main consideration of potential depletion introduced at the technology level for intensity scaling. The optimal threshold intensity is selected based on the switching and leakage undercurrent settings. The study of Another 4bit Serial Input Parallel Output (SIPO) shift register named SeriesStacking in Portable Count Depletion Shift Register (STCRSR) is developed to uphold the capability of outlined cleat plot.

## Keywords—Shift Register, CMOS, Low Potential

#### I. INTRODUCTION

A few decades ago, speed, cost and path surface were the primary concerns of VLSI field engineers. Lowest potential depletion in electronic tool lot. The only concern concerns the implantable sector in medical electronics, where high potential depletion is a disadvantage. With the development of the advancement of technology, there is an increase in the degree of integration from small to large and then very large (Rabaey & Pedram 1996). This increasing level of integration, coupled with technology that actively moves into sub-micrometer deep operating regions to improve performance, leads to a steady increase in potential energy depletion (Borkar 1999; Yeap 1998). This has become an issue of concern when the pipeline has a higher tool density and a higher frequency of work (Borkar 1999; Kang & Leblebici 2003). The rapid increase in the use of hand-held consumer electronic tools and environmental concerns regarding power supplies add to the need to reduce potential depletion in the course layout (Weste & Harris 2011). Therefore, low power depletion is one of the most important challenges of modern VLSI paths.

The dichotomy that exists in the plot of electronic tools is the simultaneous claim of high performance and low potential depletion. One of the serious challenges in the VLSI field is plotting low-potential CMOS stuff without affecting system performance. Portable density is increased due to the increasing integration of billions and billions of portable in a chip. While scaling of the tool leads to increased operating frequency, the high

potential depletion is a major drawback. As the need for reliable, faster, and low-cost products that run high-end applications grows, the need for low-potential VLSI methods is critical. Cybernated VLSI In-Domain Tracker relies on different methods and simpler solutions to enhance path performance in shorter tracking times. The main purpose of battery powered and non-battery powered tools is to minimize potential depletion. The latest graphing techniques in communication and indicator processing require higher bandwidth and higher quality noise-free indicators. Since the operating frequency increases exponentially, it is essential to conduct data processing with channels with low potential, faster and more reliably. Care should be taken when introducing potentially different management patches into the paths so as not to increase the size and cost of the paths. The real challenge is choosing the right potential depletion measures that are most appropriate to apply in a particular lot. It is very important to draw a system that takes into account all important VLSI constraints that provide reliable operation to meet speed requirements with less potential depletion and area.

# II. LITERATURE REVIEW

Partovi et al. (1996) developed the Hybrid Latch Cleat (HLFF) mainly focusing on reducing clock and latency loads. It is drawn against a clear transparent window that allows for transitions. It is almost like a pin as it provides a soft edge that allows slack to pass and reduces clock drift problems. The problem of redundant switching increases the power depletion of the system. Hybrid Latch Clear is not suitable for high speed, low potential applications. Kawaguchi & Sakurai (1998) proposed an RCSFF (Reduced Clock Swing Cleat) fabricated using a low-rotation clock driver path and a wedge element with a reduced clock-rotation technique. The clock oscillation intensity has been reduced to 1 V, thus reducing the total potential depletion to a third of that of a typical latch pad. The leakage undercurrent of the MOS portable is minimized by applying a tailgate bias. RC latency and connection potential are reduced at a higher rate than conventional batches. Klass et al. (1999) presented a group of edge-activated breakpoints of both dynamic and semi-dynamic classes that can communicate with dynamic and static path types. These pins are great for respecting the cycle time of the microprocessor. The depletion in pipeline overhead is achieved by treating each array as a single logic gate that acts as a timing element, thus removing one or more gate delays from critical paths in an array. Tschanz et al (2001) plotted an EdgeTriggered Closed Clear Pulse

Data with Output Clear (EPDCOFF) having a semidynamic architecture. It has a dynamic and static plot in the first and second stages respectively. It is located under an obvious pulse trigger pin. It has a clear pulser shared by neighboring portable, which contributes to the overall potential depletion. It has a negative setup time. This is one of the fastest clear layouts as it involves semi-dynamic layouts. It can be applied in critical paths of any graph due to its small latency. Potential depletion is high due to internal nodes charging and discharging. Fake increases potential depletion and switching noise, leading to path problems. Rasouli et al (2005) presented two modified versions of Hybrid Latch Flip flop (HLFF) named Modified Hybrid Latch Cleat (MHLFF) and Double EdgeTriggered Hybrid Latch Cleat (DMHLFF). MHLFF is a single edge triggered stop histogram and DMHLFF is a double edge histogram. MHLFF minimizes the potential depletion of the native instance by reducing unwanted internal node transitions. The two-blade version is introduced there to further reduce potential depletion. The number of stacked portable in the discharge path is reduced in both modified versions to reduce latency. Both batches have a potentially better late product. Hwang et al (2012) plotted a low potential pulse trigger pin using a conditioned pulse enhancement scheme. There is a significant depletion in the number of portable in the pulse generation logic, thus reducing the total plot area. Of the two plotting techniques, the first shorting the portable held along the discharge path using AND logic based on pass portable logic and the second dealing with possible boost condition of the discharge pulse, such that the size of the portable in the pulse path remains small. The proposed buffer chart with impulse control scheme was compared with the previous charts and the results demonstrated that this proposed chart has better results in various performance indicators. Lin (2014) presented a modified low-intensity pulse trigger pin involving a single-phase clock latch using a indicator transmission scheme from the input to the internal node of the latch that shortens the transition time, change and the activation method is clear. It has a special style in plot because True Single Phase Latch uses both pseudoNMOS logic and transmission portable logic. The long discharge path problem, one of the main problems in pulse-triggered faucets has obviously been solved here, thus achieving the full potential depletion in the system. This speed performance is accelerated and transition times are reduced. Lin et al. (2017) presented a real single-phase clock (TSPC) low potential shim called Logical Structure Depletion Engineering (LR) shims using only 19 portable. It has a master-slave architecture that uses both static CMOS logic and additional passthrough portable logic. This technique is used to minimize the total number of portable and to achieve better potential and speed results. There is no possibility of leakage due to the removal of floating buttons. An additional discharge path is provided between the main pin and the auxiliary pin which reduces switching times for better performance in the area of speed, latency and potential. Capacitive offloading is achieved by eliminating redundant paths to simplify layout.

### III. LOW POTENTIAL APPLICATION

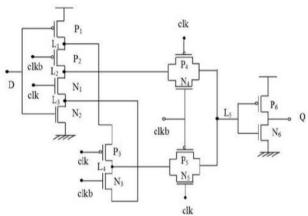

To deduce the potential in a latch, the total number of portable has been greatly reduced without affecting its performance and cell area. The architecture of the TCR shims is shown in Figure 1. Clocked portable get more attention because they contribute more to potential depletion. Since it is a dynamic double-blade trigger lock bar (DET), the two data are loaded at a specific frequency, making the frequency half of the previous data (Zhao et al 2007). Dynamic potential depletion decreases with operation.

The path has three stages, the first is a series of PMOS and NMOS portable, followed by two pass-gates and then an inverter. There are 5 intermediate nodes: L1 (between P1 & P2), L2 (between P2 & N1), L3 (between N1 & N2), L4 (between P3 & N3) and L5. Do not use series-connected inverters to produce a specific delay in a latch, but an efficient inverter is placed to prevent noise coupling. It is done using the fewest portable which reduces the parasitic effect. Intermediate nodes L2 and L4 are provided as inputs for the two transmission ports. Since the transmission port needs a two-phase clock indicator, the clock driver should not be eliminated. It also needs PMOS and NMOS portable to eliminate the same data transmission degradation as a single channel MOS portable. On the positive edge of the clock, when the input indicator is high, only P1 is blocked in the first stage and all other portable like P2, N1 and N2 are on. The width of portable P1 is increased to increase the control power. L1 and L3 are connected to the source of P3 and N4.

Two clock indicators clock (clk) and clock bar (clkb) control the path. The transmission port works in parallel with the pullup network formed by the PMOS network in the first part to increase the intermediate node by 1. This increase further reduces the worst case latency and CQ latency when clk is 1. Shorter propagation delay when working in transparent mode results in shorter setup time. The first transmission port is disabled and the data indicator at L4 is passed through the second transmission port, then an inverter to the output node. Therefore, there is no charging and discharging of the internal nodes corresponding to the variations of the input indicator at each clock cycle, thus reducing the potential. Although it is electromotive, the intensity level is not reduced much. Only two portable are directly connected to the supply intensity. The total potential dissipation of the system in equation (3.1) forms the dynamic potential (Pdyn), the static potential (Pstat) (Zhao et al 2007) and the short path potential (Pshortckt) and is given by,

$$P_{tot} = P_{dyn} + P_{stat} + P_{short-ckt}$$

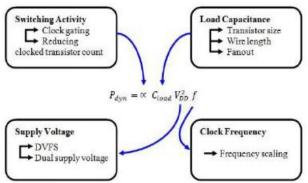

Figure 1 illustrates some popular dynamic potential depletion techniques (Panda et al 2010). Limit button switching operations by reducing the number of clocked MOS portable, clocked triggering indicators, etc. done. Using small size MOS portable with reduced capacitance in the path can minimize load capacitance. Minimizing the operating frequency and supply intensity can save more potential because the former has a linear

relationship and the latter has a quadratic relationship to the total potential.

Figure 1: Basic Structure for Dynamic Power Reduction

Here we focus more on dynamic potential dissipation. Since the number of potentially consumable conversions is minimized in TCRFF, the value of " $\alpha$ " is reduced to a large extent. So it has better dynamic saving potential. Failover of internal nodes is avoided. The speed of the clock input variants is lower than the speed of the input indicator variants. This is an additional advantage to the route in the case of potential depletion.

Figure 2: CMOS Design for Shift Register

The possibility of leakage is also calculated. The second part deals with the analysis of various timing parameters such as DQ (data out) delay, CQ (output clock) delay, hold time and setup time under intensity variations. different feeds and processes. The third part deals with calculating the layout area, total number of portable and path complexity of all cells. The potential delay products (PDPcq and PDPdq) in different conversion operations and at different processing angles are calculated in the last section. EnergyDelayProduct (EDPdq) and the leak potential of all lugs are compared. A robust comparison of graph performance was performed using MonteCarlo simulations under different processes, intensitys and temperature variations.

speed is one of the key factors that needs to be paid more attention as it plays a big role in real-time applications. On the other hand, smaller tools like clock latches are often used to develop shift registers. It has timing issues that limit the use of pulse locking in VLSI tracking. It produces false output in the later stages of the conversion because the input indicator is not transmitted correctly. Several additional paths are added between

instruments to eliminate this timing problem caused by pulse switching. While it has a good potential performance over conventional shift registers, there is an area minus as adding delay lines will maximize the total path area.

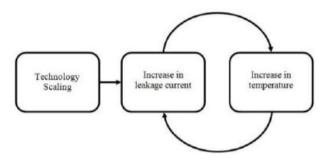

#### IV. LEAKAGE CURRENT AND TEMPATURE

Figure 3 shows the feedback mechanism between temperature and leakage undercurrent when implementing technology scaling (Panda et al. 2010). The possibility of leakage increases exponentially with temperature. A positive feedback strategy is followed where an increase in potential density increases the temperature, which further increases the potential density, creating heat escape.

Figure 3: Leakage Current and Tempature

There are various techniques to reduce the possibility of subthreshold leaks at both the path and process levels (Priya et al 2012). State saving technique The undercurrent state of the land plot can be kept. State Destruction Technique The undercurrent plot state is lost. Leak depletion techniques are also grouped according to different operating modes of the system. Active mode and standby (inactive) mode are two different modes of operation. Operation mode depletion technique aims to reduce leakage undercurrent when the path is working and in standby mode; it focuses on reducing leakage undercurrent in sleep mode. In sleep mode the MOS portable are disconnected from the potential rail by additional sleep portable to provide phantom potential rail while in active mode the different portable are properly placed in the MOS path for a stack effect to reduce leakage undercurrent.

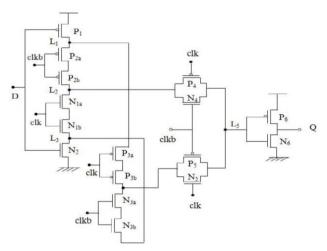

The different path-level leakage depletion techniques are VTCMOS (Variable Threshold CMOS), MTCMOS (Multi-Threshold CMOS), SCCMOS (Super Cut CMOS), IVC (Input Vector Control), Normative. Body Tendency, LECTOR (Leakage potential, Controlled Portable) etc. (Priya et al. 2012). Each technique focuses on reducing the supply intensity during no-load operation. Potential activation techniques with PMOS and NMOS portable, SCCMOS techniques, IVC are some of the most preferred methods, but they require an additional control path making the structure complex. But in the LECTOR technique, no additional control paths are used, and the size of the sleeping portable is difficult to meet the waiting requirements. Among these leakage depletion techniques, the simplest method is "portable stacking", which is one of the most

effective methods to reduce the possibility of leakage in active mode. Here, the stacking technique is applied only in the TCR latch clocked portable without affecting the logic pattern. We have a bunch of portable connected in the first stage of the TCR latch. Stacking is easy to do in this type of architecture. More leakage potential is saved by increasing the number of portable in series in the stack structure and this is based on the fact that two portable in series in the off state can cause less leakage than with a tool. When the tool is modified with a series of stacked portable placed between the potential power source and the pull-up network, it produces a small reverse bias between the source and drain terminals of the pull-up network when off, portable in series.

Figure 4: CMOS Technology for Latch

#### V. METHODOLOGY

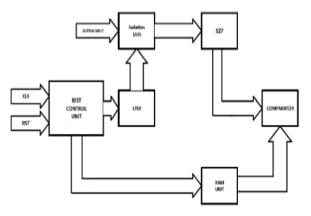

The plotting blunders that happened throughout plotting and production. Some of the necessary parameters in BIST are take a look at delay, legal responsibility coverage, check suite The BIST structure for the proposed LFSR-based prototyping is proven in Figure 1. The BIST consists of each the take a look at prototyping circuit and the circuit beneath test. The cutting-edge is remarks the identical for the different section from D2 to D12. The output is taken from the first flip-flop to the closing flip-flop, i.e. from S0 to S12. The comments sign is taken from the third flip-flop (S2), the 12 alerts to four indicators that are appropriate for the preferred s27 circuit beneath test.

Figure 5: Standard Circuit

#### a. Testing

In order to evaluate the performance of various sequential and combinatorial paths, the trendy paths are utilized. In ISCAS85, the combinational circuits C432, C499, C880, C1355, C1908, C2670, C3540, C5315, C6288, and C7552 are the most frequently used. Trendy routes have been used by some VLSI manufacturing companies to examine their products. They typically follow one of two kinds of paths: a sequential circuit and a combinational direction. Similarly, ISCAS89 is the sequential path that is utilized the most frequently. According to Lakshmi Divya and Praveen Kumar (2014), the majority of the time, these well-known paths are made use of to test functions and generate prototypes. S27 is one of the ISCAS89 paths for checking prototypes.

A shift D and common sense gates such as NNAD, AND, OR, NOR, and NOT gates make up the well-known sequencer circuit. A NAND gate number, an AND gate number, two OR gate numbers, four NOR gate numbers, and two NOT gate numbers are the three variable D numbers. Circuit s27 is a compass circuit and has 4 contributions to create one result. The layout of circuit s27 includes 13 logical changes and gates. Provides an easy demonstration of the connections between the input and output signs.

The most popular circuit is the one below the check. The s27 sequencer is the most well-known circuit. Xilinx ISE8.2-based code can be used to represent the widespread circuit. The following is the general encoding of the s27 circuit:

## b. Coding for the Preferred Circuit

From the enter seed, the LFSR shape produces 12 outputs. Additionally, 12-bit inputs can be converted to 4-bit outputs using isolates. The s27 circuit receives the 4-bit output as input. An output will be produced by circuit s27. The circuit under examination has a one-bit output. This bit can be either 0 or 1, or X. In contrast to the memory-stored reference signature, the response signature is unique. The reference mark is also perceived as the brilliant mark. If the answer signature and the golden signature match, the circuit is no longer responsible; otherwise, the circuit is. In the past, Xilinx ISE 8.2 was used to develop the coding for this evaluation. The encoding of the comparator is shown below.

Comparator encoded data:

Algorithm for Code Sample Program Programming Prototyping can be completed using LFSR. The look at vector is produced by the 12-bit LFSR. Cryptographic development makes use of the Xilinx ISE 8.2 model. The steps that an algorithm takes to generate look at vectors for s27 are listed below.

Step 1: Give the LFSR a name. module

Step 2: Set the clock and reset as input Set LFSR yield wide assortment to 12.

Step 3: Set D flip-flop 1 to 12 the outputs should be defined as S0, S1, S2, S9, S10, and S11.

Step 4: Determine the section to return

Stage 5: Allot shift yield D as LFSR yield.

Step 6: Stop. Xilinx uses coding to carry out the LFSR algorithmic steps.

The following contains the codes for the aforementioned algorithm.

#### c. Encode

module lfsr4 (clock, reset, and lfsrout); reset, input clock; output lfsrout [3:0]; back cable; wires s0 through s3; dff1 10 (s0 for clock, reset, and response); dff1 11 (s0, s1) (clock, reset); dff1 12 (s1, s2), reset, and clock; dff1 13 (s2, s3, reset, clock); assign the response as (s3-s2); define lfsrout as s0, s1, s2, s3;

The simulation model employs a standard circuit for the final module's results and discussion. The sim model also makes use of prototyping with LFSR. The LFSR uses two inputs, such as reset and clock. An isolator connects the LFSR's 12 output strains to the well-known circuit. The LFSR, CUT and in excess of a couple of modules of the LFSR are demonstrated. The scanner circuit is the most popular s27 circuit. There are four components in the common circuit.

## VI. CONCLUSION

Here, a simple double-blade dynamic shim called Portable Count Depletion Shim is provided for extremely low potential applications. The plot consists of pass gates and has the fewest clocked portable. The plot is such that offload the high capacitance and switching operation of the internal nodes. With reduced charging and discharging of internal nodes with input indicator variations, potential power depletion is further reduced. It focuses on reducing dynamic potential. It uses a double-edge activation technique that reduces the operating frequency to half of its original value, resulting in reduced dynamic potential depletion.

## REFERENCES

- [1] Absel, Kalarikkal, Manuel, Lijo and Kavitha, R. K, "Dynamic low-potential two-node pulse matching slot with efficient embedded logic", IEEE Transactions on Very Large Scale Integration (VLSI), vol. 21, no. 9, pp.1693–1704, 2013.

- [2] Alioto, Massimo, Consoli, Elio and Palumbo, Gaetano, "General Strategies for tracing the nanoscale stopper in the energy hysteresis space", IEEE Transactions on Paths and Systems I: Papers Usually, practice. 57, No. 7, pp.1583–96, 2010.

- [3] Awad, Ahmed, Takahashi, Atsushi, Tanaka, Satoshi and Kodama, Chikaaki, "A Rapid Breakthrough in Masked Escalation Accounting for Process Variations with New Intensity Modeling", IEEE Transactions on Systems very

- large scale integrated data systems (VLSI), vol. 25, no. 3, p. 998–1011, 2016.

- [4] Bhattacharjee, Pritam & Majumder, Alak, "A sturdy, change-sensitive enclosed wedge for a potentially stressed FSM application", Journal of Paths, Systems and Computing, vol. 28, no 7, trang 120, 2018.

- [5] Borkar, Shekhar, "Plot Challenges of Technology Scaling", IEEE Micro, tập. 19, không. 4, tr. 23–29, 1999.

- [6] Butzen, PF & Ribas, RP 2006, "Leakage Undercurrent in CMOS SubMicrometer Gate", Universidade Federal do Rio Grande do Sul, pp. 1–30, 2006.

- [7] Chen, Jianli, Liu, Yan, Zhu, Ziran and Zhu, Wenxing, "An adaptive hybrid memetic breakthrough for VLSI floor planning without ThermalAware slicing", Integration, VLSI Journal, vol. 58, 245–252, 2017.

- [8] Chinnery, David & Keutzer, Kurt, "An overview of factors influencing potential depletion to bridge the potential gap between ASICs and custom: Tools and techniques for low-potential plotting", New York, Springer, ch. 2, p.1163–1170, 2007.

- [9] Chung, Wai, Lo, Timothy and Sachdev, Manoj, "A Comparative Analysis of Low-potential, Low-Intensity Triggered Latches", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 10, no. 6, p. 913–918, 2002.

- [10] Consoli, Elio, Alioto, Massimo, Palumbo, Gaetano et Rabaey, January, "Conditional PushPull pins with 726fJPs Energy Delay product in 65nm CMOS", Synthesis of Solids Pathway Conference technical papers IEEE International, vol. 55, no. 8, 482–83, 2012.

- [11] Correia, Sérgio, Beko, Marko, Cruz, Luís et Tomic, Slavisa juillet, "Elephant Herding Escalation for EnergyBased Localization", Sensors, vol. 18, no. 2849, pp.1–14, 2018.

- [12] Darwish, T & Bayoumi, M, "Reducing modified SAFF cleat conversion for low-potential applications", Proceedings of the International Conference on Microelectronics, ICM, pp. 96–99, 2002.

- [13] Dash, Judhisthir, Dam, Bivas and Swain, Rajkishore, "Optimal plotting of linear multiphase band stopping filters using advanced cuckoo seed search swarm enhancement", Journal of Soft Computing application, flight. 52, p. 435–45, 2017.

- [14] Dehbashian, Maryam & MaymandiNejad, Mohammad, "Innovative Expansion Core for Analog Circuit Layout Automation Using Miniature Circles", Engineering Applications of Artificial Intelligence, flight. 58, p. 62–78, 2017.

- [15] Firdous, Ayesha, Anand, M, & Rajan, B, "Diagram and implementation of advanced leak depletion techniques in VLSI CMOS paths", vol. 12, no. 2, pp.155–60, 2017.