# EV Charging System with V2G Operation using 5-Level Multi-level Inverter

Sharma Rahul Ranjukumar<sup>1</sup>, Priyanka Maheshwari<sup>2</sup> M. Tech Scholar, Department of Electrical Engineering, RKDF University, Bhopal, India<sup>1</sup> Assistant Professor, Department of Electrical Engineering, RKDF University, Bhopal, India<sup>2</sup>

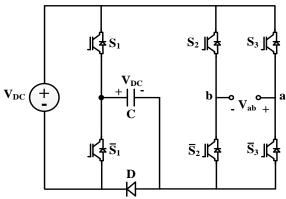

Abstract— MLIs have a significant advantage over twoinverters, including lower dv/dt, improved harmonic electromagnetic interference, performance and reduced output filter size. NPC inverter, FC inverter and CHB inverters are three of the earliest well-established inverter topologies that have been around for a long time. These conventional topologies each have their own set of advantages and disadvantages. In the case of NPC and FC suffer the capacitor voltage balancing issues and require a complex control strategy to balance the capacitor voltage. Six unidirectional switches, one diode, and one capacitor with a PV source are used. In this topology, a leg of the switched capacitor is cascaded with the H-bridge structure. The capacitor (C) is charged to the DC input voltage of  $V_{DC}$ . The proposed inverter generates different output levels of 0,  $\pm V_{DC}$ , and  $\pm 2V_{DC}$ . It archive five-voltage level at the output terminal and generates boost output voltage with levels of +200V, +100V, 0, -100V and -200V.

Keywords— Multi-level Inverter, 5-level, Boost Factor, Switched Capacitor

#### I. INTRODUCTION

Power electronics and processors play an important role in motor control, light control, heat control, power supplies, the vehicle system, HVDC, FACTS, and renewable applications in contemporary technology. The way of thinking centers around protecting the energy and satisfying the power need precisely and the power modulator relating to inverter/converter innovation satisfies the prerequisites and this draws in the specialists to investigate in the inverter field. The previously mentioned applications work in the scope of medium power, high power at a higher voltage. With the assistance of semiconductor gadget innovation, power converters are to be planned with higher working voltage. As a solitary gadget neglects to help such high voltages, various gadgets need to interface in series to meet the voltage rating. One more test in the modern area is the necessity and support of the sinusoidal power supply with variable voltage and recurrence. The introduction of inverters alleviates the aforementioned drawbacks. Through a control mechanism and seriesconnected switches in inverters, high voltage rating voltage stress is distributed among the series switches, reducing losses. Because of benefit of least misfortunes, inverters is likewise utilized for medium voltage applications. When a classical square wave inverter

operates at a higher voltage, the dominant harmonics are introduced, affecting the inverter's front-end and loadside performance significantly. Even though passive filters are used to find a solution, the loss is bigger and takes up more space. The elective way is given by Staggered Inverters (MLI) [1, 2]. Through a switching sequence, MLI generates a sinusoidal voltage waveform in the form of voltage steps. Different benefits of MLI are decreased electromagnetic impedance, diminished current bending, great quality voltage waveform, great current waveform. The fundamental sorts of MLI are unbiased point cinched MLI, flying capacitor MLI and flowed H-span MLI. To incorporate almost sinusoidal voltage, larger number of levels should be produced with the assistance of more number of switches, more number of sources and more number of entryway drivers [3, 4]. As a result, the efficiency declines as the number of switches in the transmission path increases.

### II. PROPOSED METHODOLOGY

An exhaustive assessment of the literature is presented with the goal of decreasing the number of devices required to support an increased number of output levels. In this section, the thesis objectives and structure are discussed in detail. Nowadays, investments in new renewable and sustainable energy sectors are being rapidly carried out to reduce CO2 emissions and address global warming caused by the use of fossil fuels.

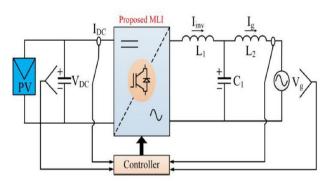

Fig. 1: Proposed Methodology

Advances in power electronics have contributed greatly to the advent of solar photovoltaic and wind energy-based power generation systems. In order to connect is these sources to the distribution grid and/or local loads. Basic application of proposed work is shown in figure 1. MLIs have a significant advantage over two-level inverters, including lower dv/dt, less electromagnetic

interference, improved harmonic performance and reduced output filter size. NPC inverter, FC inverter and CHB inverters are three of the earliest well-established inverter topologies that have been around for a long time. These conventional topologies each have their own set of advantages and disadvantages. In the case of NPC and FC suffer the capacitor voltage balancing issues and require a complex control strategy to balance the capacitor voltage. The number of clamping diodes and capacitors required increases as the voltage levels increase. To synthesize a multistep voltage waveform, Separate dc sources are required for the CHB inverter and consequently, the voltage gain in all the classical topologies is limited to one. To address these difficulties, the concept of switched DC source and reduced device count to maximize the voltage level have been investigated, as they provide a compact architecture that reduces the systems cost and control complexity. Existing topologies have the problem of voltage boosting capabilities. Novel topologies based on a Switched Capacitor (SC) are being researched to improve boosting ability and significantly reduce the number of devices further. Figure 2 shows the proposed five-level boosting inverter topology.

Fig. 2: 5-level Inverter

#### **Boost Inverter**

The operational states and capacitor parallel and series path (i.e., charging and discharging) for the proposed 5-Level inverter for a grid-connected PV power generation are shown in Table 1. It's worth noting that 1 and 0 represent the ON and OFF states of the power switches. "A" and "V" indicate the charging and discharging modes of the capacitor 'C'. The path through which capacitors are charged is shown in green, and the resistive load and inductive load current path are shown in blue and red.

Table 1: Switching table of proposed boost inverter

| Switching State | V <sub>ab</sub> | Power Switches |                       |       |                     |       |                     | Capacitors (C) |

|-----------------|-----------------|----------------|-----------------------|-------|---------------------|-------|---------------------|----------------|

|                 |                 | $S_1$          | $\overline{S}_{1} \\$ | $S_2$ | $\overline{S}_2 \\$ | $S_3$ | $\overline{S}_3 \\$ |                |

| $\mu_1$         | 0               | 1              | 0                     | 1     | 0                   | 1     | 0                   | Δ              |

| $\mu_2$         | $+V_{DC}$       | 1              | 0                     | 0     | 1                   | 1     | 0                   | Δ              |

| $\mu_3$         | $+2V_{DC}$      | 0              | 1                     | 0     | 1                   | 1     | 0                   | $\nabla$       |

| $\mu_4$         | 0               | 1              | 0                     | 0     | 1                   | 0     | 1                   | Δ              |

| $\mu_5$         | $-V_{DC}$       | 1              | 0                     | 1     | 0                   | 0     | 1                   | Δ              |

| $\mu_6$         | $-2V_{DC}$      | 0              | 1                     | 1     | 0                   | 0     | 1                   | $\nabla$       |

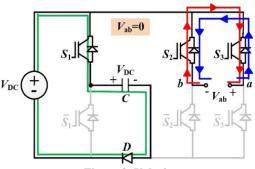

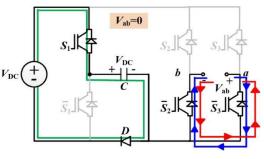

Vab=0: It defines states μ1 and μ4. As shown in Figure 3 and Figure 4.4 zero-voltage state across the load in which switches S1, S2 and S3 or S1,  $\overline{S2}$  and  $\overline{S3}$  are ON, while turning OFF  $\overline{S1}$ ,  $\overline{S2}$  and  $\overline{S3}$  or  $\overline{S1}$ ,S2 and S3. As a result of being in parallel with the DC supply, the capacitor C gets charged to voltage  $V_{DC}$  through the switch S1.

Figure 3: Vab=0

Figure 4: Vab=0

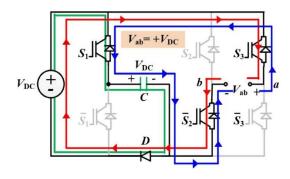

<u>Vab=+VDC</u>: As depicted in figure 4, power devices S1,  $\overline{S2}$  and S3 are conducting while  $\overline{S1}$ , S2 and  $\overline{S3}$  are OFF. The capacitor C is charged to the VDC by parallel connection with the source. This operation defines the state μ2.

Figure 5: Vab=+ $V_{DC}$

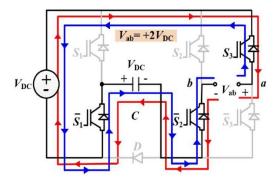

Vab= +2VDC: It defines state  $\mu 3$ . In this state, shown in figure 5, power devices  $\overline{S1}$ ,  $\overline{S2}$  and S3 are conducting while S1, S2 and  $\overline{S3}$  are OFF. In this state, by turning ON the switch  $\overline{S1}$  capacitor C appears in series with the DC source and gets discharged.

Figure 6: Vab=+2V<sub>DC</sub>

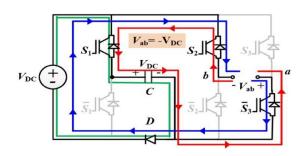

**Vab= -VDC:** It defines state  $\mu 5$ . By turning ON S1 Capacitor C appeared across the DC source and got charged to voltage VDC. The level -VDC is achieved when power switches S1, S2 and  $\overline{S3}$  conduct while turning OFF  $\overline{S1}$ ,  $\overline{S2}$  and S3. This state is shown in figure 7.

Figure 7: Vab=-V<sub>DC</sub>

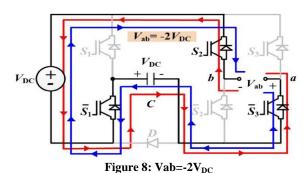

Vab= -2VDC: In this state, as shown in figure 8, by turning ON the switch  $\overline{S1}$  capacitor C appears in series with the source and gets discharged. The -2VDC level is achieved by conducting power switches  $\overline{S1}$ , S2 and  $\overline{S3}$  while turning OFF S1,  $\overline{S2}$  and S3. This operation defines the state μ6.

# III. SIMULATION RESULT

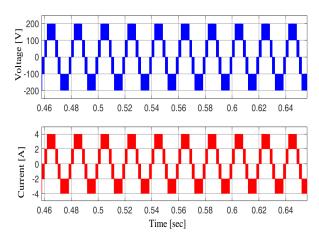

Figure 9 shows the load voltage and load current with resistive load of 50 Ohm. It archive five-voltage level at the output terminal and generates boost output voltage with levels of +200V, +100V, 0, -100V and -200V.

Figure 9: Output voltage and current with resistive load

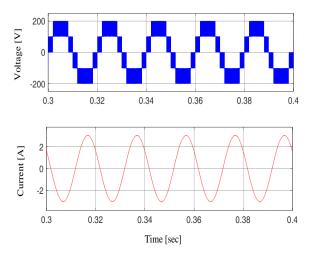

Figure 10: Output voltage and current with inductive load

Figure 10 shows the load voltage and load current with inductive load of 50 Ohm and 100mH. It archives five-voltage level at the output terminal and generates boost output voltage with levels of +200V, +100V, 0, -100V and -200V. Also, generates pure sinusoidal current at the output load terminal.

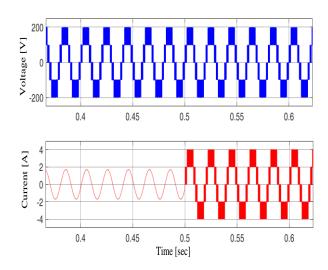

Figure 11: Output voltage and current with inductive load change to resistive load

Figure 11 shows the dynamic response of the proposed multilevel inverter. In this intense the inductive load change from 1000hm 100mH to pure resistive load 500hm at the time of 0.5sec. It can be clearly seen that the output voltage has not change at this time but output current has been doubled at this point. Its changes from 1.8A inductive current to the 4A resistive current after doing change the load.

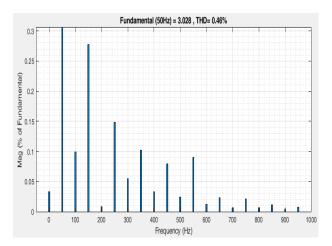

Figure 12 shows the Total harmonic profile (THD) of the output current. Its achieves a minimum value of the THD i.e., 0.46% that is good enough to use for the grid and also can be used for the different load applications.

Figure 12: Total harmonic distortion (THD) profile of output current

## IV. CONCLUSION

To generate a PWM signal, high-frequency triangular signals are compared with the sinusoidal reference. The resulting pulses are used to switch devices corresponding to various voltage levels. As depicted in figure 4.8, waveforms  $Vcr\alpha\{\alpha=1\text{ to }2\}$  of the similar frequency (fcr), phase angle, and maximum peak value (Acr) are utilized for carriers. The voltage controller generates a reference signal (Vref) with amplitude (Aref) and frequency (fref). The absolute value |Vref| is compared to the high-frequency triangle signal Vcr1 to Vcr2 with a similar frequency and phase angle.

When it is connected in series with the load, it releases its stored energy. Several charging durations of the capacitor occur during one cycle of the output voltage and capacitor voltages can dynamically maintain the source voltage, with some voltage ripples. This feature enables automatic balancing of the capacitor voltage. Capacitance discharge values are dependent on the load, the longest discharge time and the load power factor.

#### REFRENCES

- [1] Vikram Singh, Loveleen Kaur, Jagdish Kumar and Amrita Singh, "Solar PV Tied Electric Vehicle Charging System using Bidirectional DC-DC Converter", Second International Conference on Power, Control and Computing Technologies (ICPC2T), IEEE 2022.

- [2] Suraj S, Narayan S. Manjarekar and Soumyabrata Barik, "Switched Capacitor Based Bidirectional DC-DC Converter for Photovoltaic Energy Storage System in Indian Electricity Demand Scenario Utilizing Secondary Life of Electric Vehicle Battery", IEEE International Conference on Power Electronics, Drives and Energy Systems (PEDES), IEEE 2022.

- [3] Abdalrahman Elshora, Yasser Elsayed and Hossam A. Gabbar, "Modular Bidirectional Converter with Multiple Power Sources for Fast Charging of Electric Vehicles", IEEE 9th International Conference on Smart Energy Grid Engineering (SEGE), IEEE 2021.

- [4] Y. Q. Wang Y. S. Yuan G. Li Y. M. Ye K. W. Wang and J. Liang "A T-type switched-capacitor multilevel inverter with low voltage stress and self-balancing" IEEE Transactions on Circuits and Systems I: Regular Papers vol. 68 no. 5 pp. 2257-2270 May 2021.

- [5] Vivek Kumar Singh, Yogesh Sahu, Praveen Kumar Mishra, Prabhakar Tiwari and Rakesh Maurya, "Charging of Electric Vehicles Battery using Bidirect ional Converter", International Conference on Electrical and Electronics Engineering (ICE3), IEEE 2020.

- [6] S. Athikkal C. Bharatiraja B. Lehman and T. B. Lazzarin "Performance Evaluation of A Dual Input Hybrid Step up DC-DC Converter" 2020 International Conference on Power Instrumentation Control and Computing (PICC) 2020.

- [7] Y. Jeong J. Park R. Rorrer K. Kim and B. Lee "A Novel Multi-input and Single-output DC/DC Converter for Small Unmanned Aerial Vehicle" 2020 IEEE Applied Power Electronics Conference and Exposition (APEC) 2020.

- [8] Y. Q. Wang Y. S. Yuan G. Li T. J. Chen K. W. Wang and J. Liang "A generalized multilevel inverter based on T-type switched capacitor module with reduced devices" Energies vol. 13 no. 17 pp. 4406 Aug. 2020.

- [9] S. Habib M. M. Khan F. Abbas A. Ali M. T. Faiz F. Ehsan et al. "Contemporary trends in power electronics converters for charging solutions of electric vehicles" CSEE Journal of Power and Energy Systems vol. 6 no. 4 pp. 911-929 Dec. 2020.

- [10] J. Zeng W. J. Lin D. H. Cen and J. F. Liu "Novel K-type multilevel inverter with reduced components and self-balance" IEEE Journal of Emerging and Selected Topics in Power Electronics vol. 8 no. 4 pp. 4343-4354 Dec. 2020.

- [11] S. A. Gorji H. G. Sahebi M. Movahed and M. Ektesabi "Multi-Input Boost DC-DC Converter with Continuous Input-Output Current for Renewable Energy Systems" 2019 IEEE 4th International Future Energy Electronics Conference (IFEEC) pp. 1-5 2019

- [12] H. AboReada S. S. Williamson and V. Sood "Analysis and Control of Multi-Input Single-Output Non-Isolated DC/DC Converter for Effective Renewable Energy Management" 2019 IEEE Transportation Electrification Conference and Expo (ITEC) pp. 1-6 2019.

- [13] W. J. Lin J. Zeng J. F. Liu Z. X. Yan and R. J. Hu "Generalized symmetrical step-up multilevel inverter using crisscross capacitor units" IEEE Transactions on Industrial Electronics vol. 67 no. 9 pp. 7439-7450 Sep. 2020.

- [14] K. P. Panda P. R. Bana and G. Panda "A switched-capacitor self-balanced high-gain multilevel inverter employing a single DC source" IEEE Transactions on Circuits and Systems II: Express Briefs vol. 67 no. 12 pp. 3192-3196 Dec. 2020.

- [15] M. Ghodsi and S. M. Barakati "New generalized topologies of asym-metric modular multilevel inverter based on six-switch H-bridge" Inter-national Journal of Circuit Theory and Applications vol. 48 no. 5 pp. 789-808 May 2020.

- [16] M. Ghodsi and S. M. Barakati "A generalized cascade switched-capacitor multilevel converter structure and its optimization analysis" IEEE Journal of Emerging and Selected Topics in Power Electronics vol. 8 no. 4 pp. 4306-4317 Dec. 2020.

- [17] AbderezakLashab, Dezso Sera, Frederik Hahn, Luis Camurca, YacineTerriche, Marco Liserre, and Josep M. Guerrero, "Cascaded Multilevel PV Inverter With Improved Harmonic Performance During Power Imbalance Between Power Cells", IEEE Transactions on Industry Applications, Vol. 56, No. 3, May/June 2020.